基于EDA技术的计算机硬件系统设计方案

随着信息技术的飞速发展,计算机硬件系统的复杂度和性能要求日益提升。传统的硬件设计方法,如手工绘图与分立元器件搭建,已难以满足现代计算机系统在集成度、可靠性和开发效率上的需求。在这一背景下,电子设计自动化(EDA)技术应运而生,并已成为计算机硬件系统设计的核心支撑技术。本文将探讨基于EDA技术的计算机硬件系统设计方案,阐述其关键流程、核心优势以及未来发展趋势。

一、EDA技术概述

EDA技术是指利用计算机软件工具,完成电子系统或集成电路的功能设计、逻辑综合、物理设计、仿真验证等一系列自动化流程的技术集合。它涵盖了从系统级、寄存器传输级(RTL)到门级和物理级的全流程设计。对于计算机硬件系统而言,EDA工具使得从中央处理器(CPU)、内存控制器、高速总线到各类外设接口的复杂设计成为可能。

二、基于EDA的计算机硬件系统设计流程

一个完整的基于EDA的硬件系统设计,通常遵循以下结构化流程:

- 系统架构与规格定义:根据计算机系统的目标(如通用计算、嵌入式应用、高性能计算等),确定硬件系统的整体架构、性能指标、功耗预算和接口规范。这通常在高级建模语言或系统级设计工具中进行。

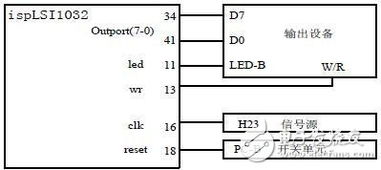

- RTL设计与硬件描述语言(HDL):使用硬件描述语言(如VHDL或Verilog)对系统的数字逻辑部分进行行为级或寄存器传输级描述。这一阶段将抽象的架构转化为可综合的逻辑电路描述,是设计的核心环节。

- 功能仿真与验证:利用EDA仿真工具(如ModelSim、VCS等),对RTL代码进行严格的仿真测试,验证其功能是否符合规格定义。验证是确保设计正确的关键,通常占据整个设计周期的绝大部分时间。

- 逻辑综合:使用综合工具(如Design Compiler),将RTL描述在特定工艺库(如台积电7nm库)的约束下,转换为优化的门级网表。这一步骤实现了从行为描述到实际物理逻辑的映射。

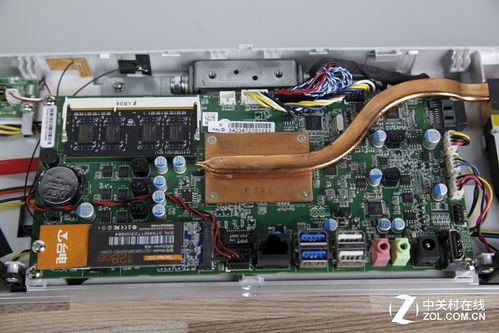

- 物理设计(布局布线):将综合后的门级网表导入后端物理设计工具(如IC Compiler、Innovus)。此阶段完成芯片的布局规划、单元摆放、时钟树综合以及全局与细节布线,生成最终的版图(GDSII文件)。对于板级系统,则对应着PCB布局布线工具(如Cadence Allegro)。

- 时序分析与后仿真:在物理设计后,提取版图的寄生参数,进行精确的时序分析和后仿真,确保电路在目标工艺和环境下能满足所有时序要求(建立时间、保持时间)。

- 制造与测试:将最终的版图数据交付给芯片制造厂(Foundry)进行流片生产,或生成PCB制板文件进行电路板生产。对生产出的硬件原型进行实测与调试。

三、设计方案的核心优势

采用EDA技术进行计算机硬件系统设计,相比传统方法具有显著优势:

- 设计效率与自动化程度高:自动化工具替代了大量重复性手工劳动,如逻辑优化、布局布线,极大缩短了设计周期。

- 设计复杂度的可管理性:EDA工具强大的处理能力使得设计包含数亿甚至数十亿晶体管的复杂片上系统(SoC)成为可能,这是手工设计无法想象的。

- 设计质量的保证:通过多层次、多角度的仿真验证和形式验证,能够在设计早期发现并修正错误,降低了后期流片失败的风险和成本。

- 性能与功耗的优化:综合与布局布线工具可以根据严格的时序、面积和功耗约束进行自动优化,帮助设计者达到最佳的能效比。

- 支持IP复用与模块化设计:EDA环境促进了硬件知识产权(IP)核(如CPU核、DDR控制器、PCIe接口等)的复用,实现了“搭积木”式的快速系统构建,加速了产品上市时间。

四、挑战与未来发展趋势

尽管EDA技术已非常成熟,但面对后摩尔时代计算机硬件的新需求,仍面临诸多挑战与发展机遇:

- 异构计算与系统级协同设计:未来的计算机系统往往是包含CPU、GPU、FPGA、AI加速器在内的异构系统。EDA工具需要向更高层次的系统级设计、软硬件协同设计与验证平台演进。

- 功耗与热管理的极致优化:随着芯片功耗密度不断增加,功耗完整性分析、低功耗设计(如电源门控、多电压域)以及热分析将成为EDA流程中不可或缺的一环。

- 先进封装与Chiplet集成:基于硅中介层、3D堆叠等先进封装技术的Chiplet(小芯片)设计范式,要求EDA工具支持多物理域(电、热、力)的协同设计与分析。

- 人工智能与EDA的融合:将机器学习/人工智能技术引入EDA工具,用于优化布局、预测时序、加速验证等,是当前的重要研究方向,有望带来设计效率的又一次飞跃。

###

EDA技术是现代计算机硬件系统设计的基石。一套科学、完整的基于EDA的设计方案,不仅涵盖了从概念到实物的全流程自动化实现,更通过其强大的仿真、验证与优化能力,确保了硬件系统在性能、功耗、可靠性和成本上的最优平衡。随着计算需求的不断演进和工艺技术的持续进步,EDA技术自身也将不断革新,持续赋能更强大、更智能的计算机硬件系统诞生。

如若转载,请注明出处:http://www.baomaplan.com/product/13.html

更新时间:2026-05-06 04:52:25